Introduction:

In the pursuit of mastering Cadence Virtuoso, I recently encountered a perplexing error message: “ERROR (OSSHNL-116): Unable to descend into any of the views defined in the view list, ‘hspiceD spice cmos_sch cmos.sch schematic’, for the instance ‘X’ in cell ‘Y’. Either add one of these views to the library ‘NCSU_Analog_Parts’, cell ‘res’ or modify the view list to contain an existing view.” This blog post aims to share my experience and the steps I took to overcome this obstacle.

The Initial Encounter:

As I followed a tutorial on using ADE for circuit simulation in Cadence Virtuoso, the dreaded error message suddenly halted my progress. A quick Google search yielded only eight results, making it apparent that this might be a challenging issue to address.

Analyzing the Error:

The literal explanation seemed straightforward, suggesting that the system could not locate the specified component in the library. However, I double-checked my configuration in the cds.lib file and verified that the library was set correctly. I attempted to redraw the schematic and run the simulation, but to my dismay, the same error persisted.

A New Approach:

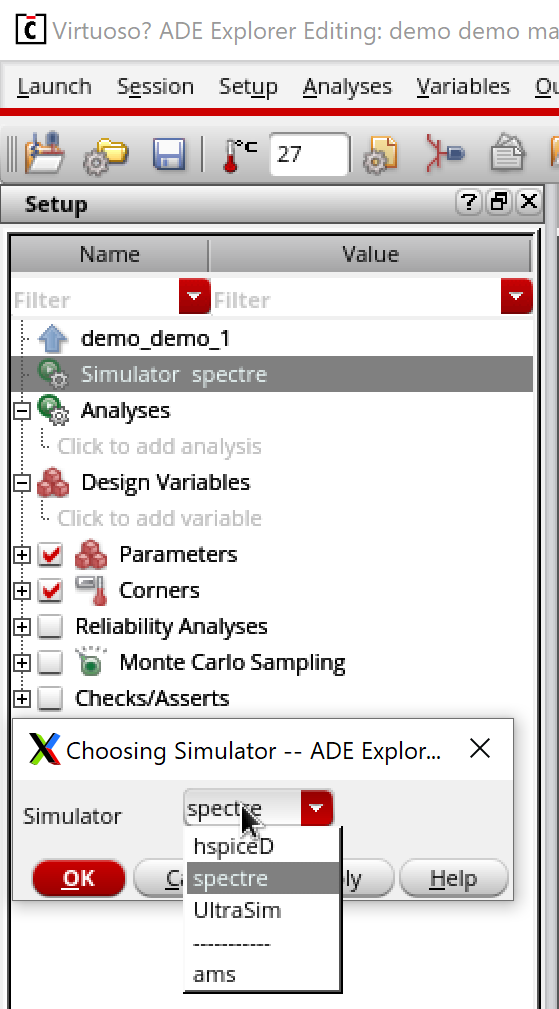

Refusing to be defeated, I decided to delve deeper into the problem. While investigating the simulator settings in ADE’s Setup -> Simulator/Directory/Host, I discovered that switching to “spectre” and “UltraSim” allowed the simulation to proceed without encountering the initial error associated with “hspiceD.”

Exploring Other Options:

I was determined to resolve the issue with “hspiceD” and decided to explore alternative simulator options. I attempted “ams,” “spectreVerilog,” and “UltraSimVerilog,” but each attempt yielded the error message: “ERROR (ADE-1093): To select ‘ams’ as the simulator in the Analog Design Environment, you must choose the config view (Setup -> Design, Choosing Design, specify the config view in the View Name field).” Intrigued by this new clue, I checked the config view and found that only “schematic” was listed. It became evident that I needed to investigate further to understand the workings of these three options.

Conclusion:

The journey to resolve the “ERROR (OSSHNL-116)” in Cadence Virtuoso proved to be an enlightening experience. Through trial and error, I managed to circumvent the issue by switching to alternative simulators. However, the lingering curiosity about the “ams,” “spectreVerilog,” and “UltraSimVerilog” options remains, inviting me to delve into their intricacies in future endeavors. My journey in Cadence Virtuoso continues, as I embrace the challenges that come my way and strive to unravel its mysteries.

Remember, the path to proficiency in any tool or software involves continuous learning and exploration. As I move forward, I look forward to conquering more hurdles and uncovering the secrets that Cadence Virtuoso holds. Stay tuned for more updates and insights in my quest to master this powerful design environment.

Leave a Reply